大板扇出型封裝,挑戰(zhàn)與機(jī)遇共存——華進(jìn)大板扇出聯(lián)合體二期項(xiàng)目即將啟動

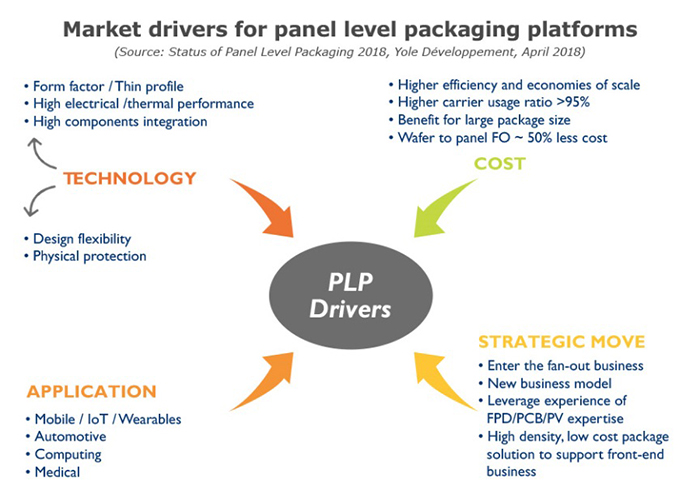

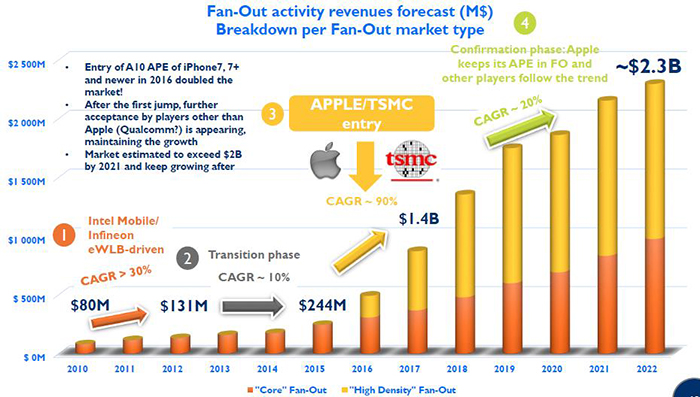

市場青睞低成本高性能產(chǎn)品,封裝解決方案不斷面臨挑戰(zhàn)與創(chuàng)新。扇出型封裝技術(shù)始于2006年,經(jīng)過十年沉淀,于2016年迎來了爆發(fā)式增長。目前,扇出型封裝主要集中在晶圓級;然而,晶圓有限的利用率及其高昂的成本阻礙其大批量制造。從晶圓級到面板級的高性能、低成本的封裝需求,驅(qū)動著半導(dǎo)體行業(yè)開發(fā)創(chuàng)新的解決方案。將晶圓級封裝轉(zhuǎn)變?yōu)榇蟪叽绨寮壏庋b成為降低整體成本的新途徑,在技術(shù)成熟的條件下,成本可降低50%,產(chǎn)品良率超過90%。事實(shí)上,板級工藝的基礎(chǔ)設(shè)施已經(jīng)引起了半導(dǎo)體行業(yè)的極大興趣,其具有成本優(yōu)勢及規(guī)模經(jīng)濟(jì)效益,是一個(gè)有前景的市場。各種因素正在推動板級扇出封裝(FOPLP)的發(fā)展,并鼓勵(lì)全產(chǎn)業(yè)鏈(包括設(shè)備和材料)投資板級扇出基礎(chǔ)設(shè)施,已經(jīng)成為各大OSAT路線圖上的重要戰(zhàn)略布局。目前主要玩家包括如ASE、SEMeCO、NEPES、Intel、SAMSUNG。

● 大板扇出型封裝的市場應(yīng)用及挑戰(zhàn)

扇出型封裝市場目前主要集中在基帶、電源管理及射頻收發(fā)器等單芯片封裝應(yīng)用以及手機(jī)應(yīng)用處理器芯片、動態(tài)存儲器芯片、車載雷達(dá)和無人駕駛等高密度多芯片堆疊封裝應(yīng)用領(lǐng)域。扇出型封裝技術(shù)正朝著諸如多芯片、薄型封裝和3D SiP這些下一代封裝方向出發(fā),不僅應(yīng)用于電子封裝,還可用于傳感器、功率IC和LED封裝等領(lǐng)域。通過大板扇出封裝技術(shù)可以獲得小尺寸、更高的集成度和功能性,其應(yīng)用領(lǐng)域包括無人機(jī)、汽車側(cè)面避碰系統(tǒng)、自動停車裝置等。

經(jīng)過多年的工藝及技術(shù)開發(fā)和驗(yàn)證,F(xiàn)OPLP終于開始進(jìn)入規(guī)模量產(chǎn)。根據(jù)Yole Développement,整體的扇出封裝市場預(yù)計(jì)會從2015年的2.44億美元增長到2022年的23億美元,F(xiàn)OPLP市場營收預(yù)計(jì)將在2023年達(dá)到約2.80億美元。Powertech Technologies(PTI)、NEPES以及SEMCO預(yù)計(jì)將在2018年底進(jìn)入FOPLP量產(chǎn)。NEPES主要瞄準(zhǔn)的是(L/S>10um)汽車、傳感器和物聯(lián)網(wǎng)相關(guān)的應(yīng)用, PTI和SEMCO的長期目標(biāo)是L/S <8/8或更小線寬線距的中高端應(yīng)用。其余各大OSAT,如ASE、Amkor、JCET/STATS CHIPPAC等,也在評估技術(shù)方案,每個(gè)玩家都在基于自己的戰(zhàn)略路線和設(shè)備設(shè)施進(jìn)行板級扇出封裝技術(shù)的研發(fā)和布局。

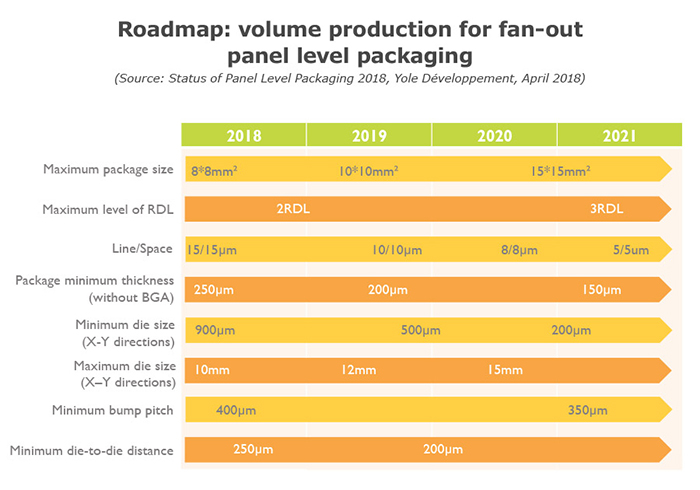

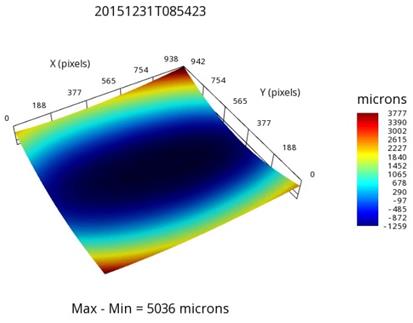

機(jī)遇與挑戰(zhàn)并存,F(xiàn)OPLP的開發(fā)及產(chǎn)業(yè)化仍存在不少挑戰(zhàn)。業(yè)界標(biāo)準(zhǔn)缺失,由于應(yīng)用領(lǐng)域和客戶不同,采用的制程及面板尺寸也不盡相同,終端用戶很難根據(jù)統(tǒng)一的標(biāo)準(zhǔn)去選擇,設(shè)備廠商也無法設(shè)計(jì)出滿足不同尺寸要求的設(shè)備,產(chǎn)線配套設(shè)施投入昂貴。此外,還有一系列技術(shù)難關(guān)需要攻克,如翹曲控制、貼片精度、在大面板上制造小于10/10um的RDL線路等。FOPLP實(shí)現(xiàn)產(chǎn)業(yè)化必須統(tǒng)一標(biāo)準(zhǔn),如板級尺寸和裝配工藝的標(biāo)準(zhǔn)化。據(jù)Yole Développement的市場調(diào)研報(bào)告,目前大多玩家支持一個(gè)相對簡單的設(shè)計(jì):L/S>10/10 um,封裝尺寸<10 x10 mm2,最多2層RDL。隨著技術(shù)和經(jīng)驗(yàn)的成熟,最終將采用高密度設(shè)計(jì):L/S <10/10 um,多層RDL,封裝尺寸>15×15 mm2和多芯片SIP集成。

FOPLP量產(chǎn)技術(shù)路線圖(圖片來自Yole Développement)

● 華進(jìn)在FOPLP的積累與發(fā)展

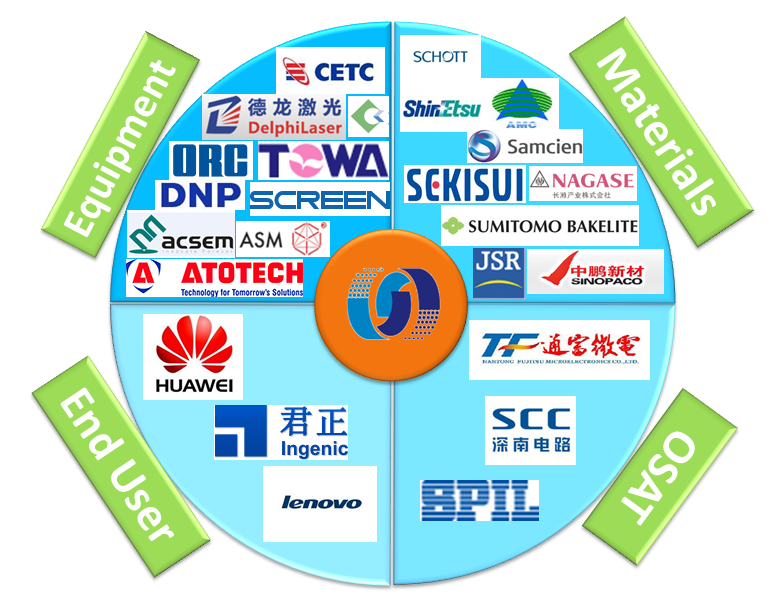

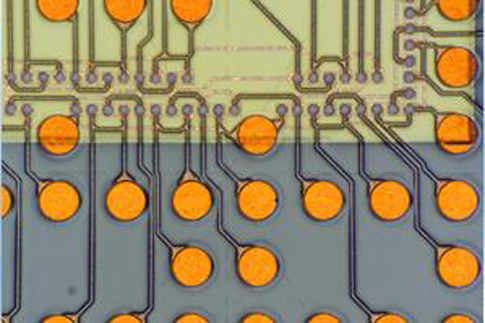

2015年,華進(jìn)聯(lián)合國內(nèi)外25家企業(yè)成立了大板扇出聯(lián)合體,主攻320mm×320mm板級扇出工藝技術(shù)的開發(fā),形成了包括終端用戶、設(shè)計(jì)、封裝代工和材料裝備于一體的完整產(chǎn)業(yè)鏈。我們的聯(lián)合體成員包括通富微電、深南電路、矽品精密、JSR、SCREEN、德龍激光、聯(lián)致科技、ASM、SCHOTT、ATOTEC、ORC、SEKISUI、住友、上海微電子、技美科技等。聯(lián)合體運(yùn)作期間,完成了單顆芯片和單層RDL設(shè)計(jì)工作,并完成了熱、機(jī)械和翹曲等的模擬和仿真工作;整合了板級扇出的產(chǎn)業(yè)鏈,開發(fā)了Die First(埋入式)和Die Last(基于基板)兩種工藝路線,完成樣品流片及可靠性驗(yàn)證;形成了大板扇出的核心知識產(chǎn)權(quán),申請了5項(xiàng)大板扇出核心專利;評估和驗(yàn)證了FOPLP聯(lián)合體成員單位的相關(guān)設(shè)備及材料,如SCREEN的SLIT coating涂布機(jī)和激光直寫曝光機(jī)、ORC的PPS光刻機(jī)、ASM的貼片機(jī)、TOWA的塑封機(jī)、AOTOTECH的電鍍機(jī)、KINGYOUP的種子層PVD濺射機(jī)、SUMITOMO的粉末塑封材料、NAGASE 的液態(tài)塑封料、JSR的光刻膠/PI/臨時(shí)鍵合材料等。項(xiàng)目成果榮獲“第十二屆(2017年)中國半導(dǎo)體創(chuàng)新產(chǎn)品和技術(shù)項(xiàng)目”。

華進(jìn)第一期大板扇出聯(lián)合體成員

華進(jìn)第一期大板扇出樣品

隨著一期聯(lián)合體接近尾聲,應(yīng)廣大成員的強(qiáng)烈需求,華進(jìn)已開始籌備二期聯(lián)合體。根據(jù)國內(nèi)外多家設(shè)備/材料供應(yīng)商的反饋,并結(jié)合華進(jìn)參與的由SEMI草擬的第一版FOPLP板級尺寸的標(biāo)準(zhǔn),二期板級尺寸定為600mm x 600mm,主攻多顆芯片和多層布線的板級扇出型封裝的技術(shù)開發(fā),培養(yǎng)一個(gè)專業(yè)的FO研發(fā)團(tuán)隊(duì),提供從設(shè)計(jì)仿真、工藝加工到可靠性分析和測試的FOPLP整體解決方案,最終目標(biāo)建立一條工藝示范線。具體工藝參數(shù)如下:

華進(jìn)二期SiP FOPLP聯(lián)合體工藝參數(shù) | |

面板尺寸 | 600mm×600mm |

最小L/S | ≤15/15um |

封裝尺寸 | ≥12mmX12mm |

I/O | 300-900 |

應(yīng)用領(lǐng)域 | MCU、電源管理、5G射頻前端芯片、高頻毫米波雷達(dá)、高端FPGA\GPU\CPU等。 |

目前二期成員仍在招募中,期待您的加入,實(shí)現(xiàn)合作共贏!詳細(xì)信息請咨詢:

華進(jìn)戰(zhàn)略部 孫經(jīng)理 0510-66679351 xuyansun@ncap-cn.com

中文

中文

English

English 蘇公網(wǎng)安備 32021402001899號

蘇公網(wǎng)安備 32021402001899號