英特爾Foveros 3D封裝技術

隨著特征縮放到達物理極限,半導體行業開始研究后摩爾技術。在此領域,無論光刻技術節點,還是7納米傳統集成電路、28納米射頻集成電路,多芯片封裝對于在小形狀因子中集成多種功能是至關重要的。所有這些都必須確保低成本并在短時間內上市。以此來看,Intel已經開發了幾種互連技術以實現小芯片(chiplet)的異構集成。早在2018年,人們就在英特爾處理器上看到了這一技術的雛形,當時稱為嵌入式多芯片互連橋(EMiB)。今天,英特爾展示了另一種在處理器中使用有源轉接板和Foveros技術進行芯片互連的方案。

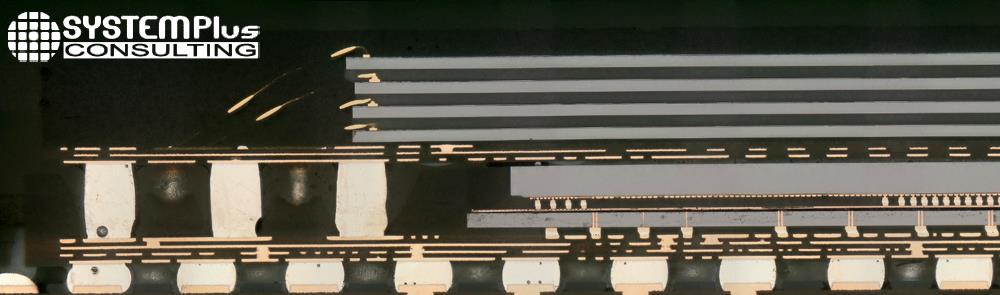

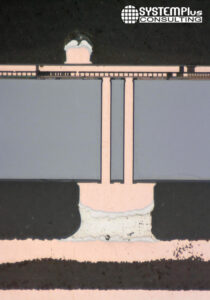

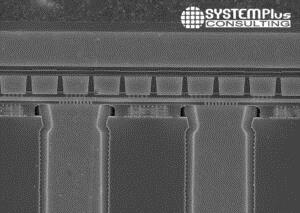

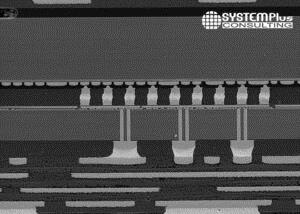

Foveros允許3D面對面(F-F)堆疊,通過使用硅通孔(TSV)在有源轉接板上集成不同類型的器件。轉接板作為不同小芯片之間的橋梁。它也包括低功率器件,如輸入/輸出(I/O)連接和高性能邏輯功率傳輸。

本報告分析的產品為英特爾Core i5-L16G7,特色是采用了英特爾的混合封裝技術。該技術依賴于Foveros F-F芯片堆疊和PoP結構。該設計旨在將10nm運算芯片與SK Hynix LPDDR4 DRAM集成在一個PoP架構的封裝體中。該方案降低了功耗并提高了核心性能,同時降低形狀因子和Z高度,以適應超級移動應用。在該結構中,采用Foveros F-F技術和Via-Middle TSV工藝將10nm的運算芯片與22nm轉接板直接互連,這樣就可以方便地將功率傳輸到處理器芯片上。

關于Intel Foveros 3D Packaging Technology

本報告對英特爾 Core i5-L16G7處理器進行了詳盡分析,全面調研了英特爾混合封裝技術,還分析了集成在封裝體內的LPDDR4X DRAM芯片。最后,它包含了完整的成本分析和器件銷售價格預估,并與臺積電的CoWoS技術進行比較。

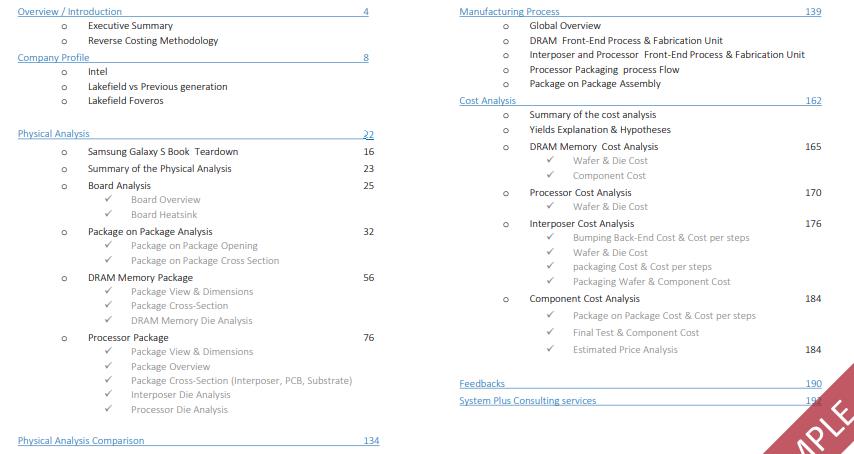

報告目錄

相關報告

Fan-Out Packaging Processes Comparison 2020

Advanced System-in-Package Technology in Apple’s AirPods Pro

Advanced packaging technology in the Apple Watch Series 4’s System-in-Package

Status of the Advanced Packaging Industry 2020

Advanced Packaging Quarterly Market Monitor

(x)PU: High-End CPU and GPU for Datacenter Applications 2020

購買方式

如需樣刊或購買報告,請聯系華進戰略部:0510-66679351 Xiaoyunzhang@ncap-cn.com

以上圖文譯自Yole Développement的Intel Foveros 3D Packaging Technology,原文請參考:

https://www.i-micronews.com/products/intel-foveros-3d-packaging-technology/

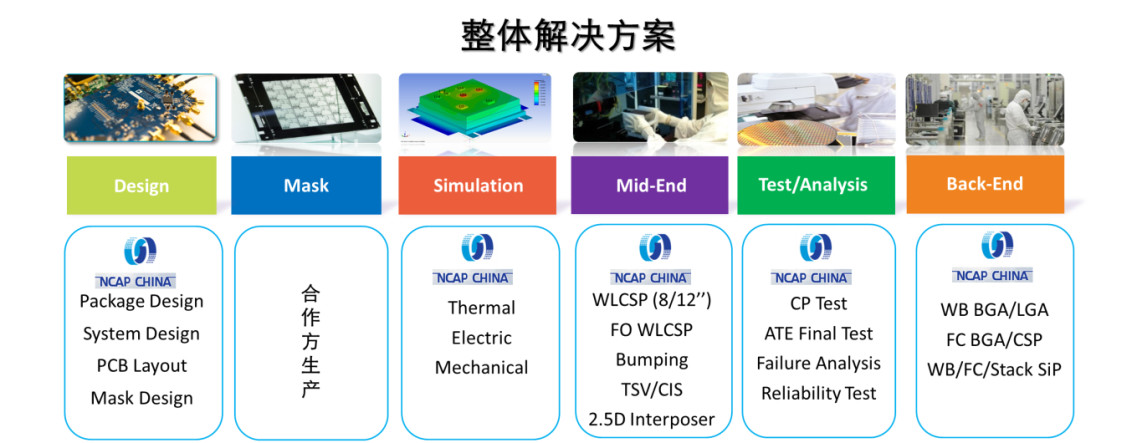

關于華進

華進半導體于2012年9月在無錫新區正式注冊成立,開展系統級封裝/集成先導技術研究,研發2.5D/3D TSV互連及集成關鍵技術(包括TSV制造、凸點制造、TSV背露、芯片堆疊等),為產業界提供系統解決方案。同時將開展多種晶圓級高密度封裝工藝(包括WLCSP/Fan-out)與SiP產品應用的研發與大規模量產,以及與封裝技術相關的材料和設備的驗證與研發。

網址:www.amcbg.com

微信:NCAP-CN

*轉載須知*

文首注明:轉載自華進半導體(ID:NCAP-CN)

閱讀原文處,請插入華進半導體原文鏈接

未經同意,不可修改文章內容

若未遵守上述規則,將按侵權處理

中文

中文

English

English 蘇公網安備 32021402001899號

蘇公網安備 32021402001899號