2.5D/3D TSV和晶圓級堆疊技術和市場報告(2019年版)

2019/03/27

(2019年2月2日發布)

(圖文譯自Yole Développement)

簡介:

2.5D異質和3D晶圓級堆疊正重塑封裝產業。華進擁有成熟先進的TSV技術,歡迎咨詢合作。

堆疊:一種不受摩爾定律限制的高度集成替代方案

隨著摩爾定律放緩,為滿足大趨勢的嚴格指標,市場開拓了新的解決方案。在封裝領域,許多半導體廠商傾向于采用2.5D和3D堆疊技術,其實TSV就是最早的堆疊技術。隨著多年的研發和對MEMS的關注,這個技術最終進入許多應用領域。如今,2.5D和3D堆疊是唯一可以滿足如AI、數據中心等應用需求的封裝方案。堆疊技術被應用于高、中、低端市場的各種硬件,包括3D堆疊存儲、圖形處理單元(GPU)、現場可編程門陣列(FPGA)和CMOS圖像傳感器(CIS)等。

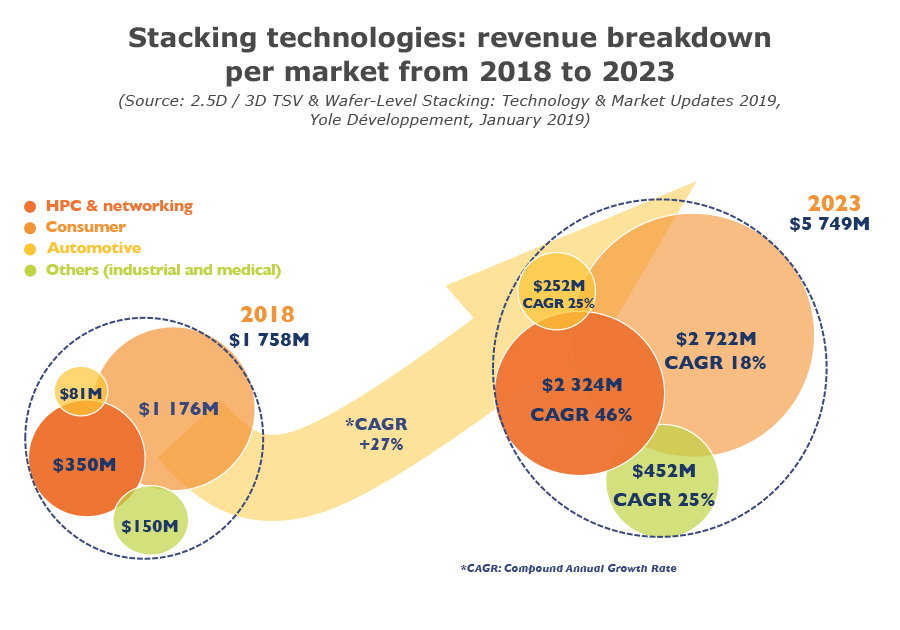

高帶寬存儲(HBM)和CIS等硬件占據了TSV的主要收入。預計2023年堆疊技術市場整體收入將超過55億美元,復合年增長率27%。現今,消費市場是******的細分市場,市場份額超65%。但這并不說明消費電子是這些技術的驅動因素。事實上,高性能計算(HPC)才是堆疊技術的真正驅動力,并呈現最快發展速度,預計市場份額將從2018年的20%迅速增長至2023年的40%。從封裝收入來看,這相當于2018年收入的6倍以上。因此,消費市場份額將減少。其他市場,如汽車、醫療、工業仍將維持現有市場份額。

2018年-2023年堆疊技術在各細分市場的預估收入

從TSV到晶圓級堆疊,封裝技術蒸蒸日上

考慮到堆疊技術競爭主要集中在TSV和“無TSV”(TSV-less)技術,Yole將在此份報告中分析這兩種技術。

在現今的高端市場,市場上最熱門的2.5D和3D集成技術就是3D堆疊存儲TSV和異質堆疊TSV轉接板。Chip-on-Wafer-on-Substrate (CoWos)技術已經廣泛應用于HPC領域,新的TSV技術將于2019年上市,如來自Intel的Foveros,基于有源TSV轉接板和3D SoC技術,還可能采用混合鍵合和TSV互連技術。從Foveros這一技術可以看出,盡管TSV面臨“無TSV”技術的挑戰,但廠商仍對它有信心。

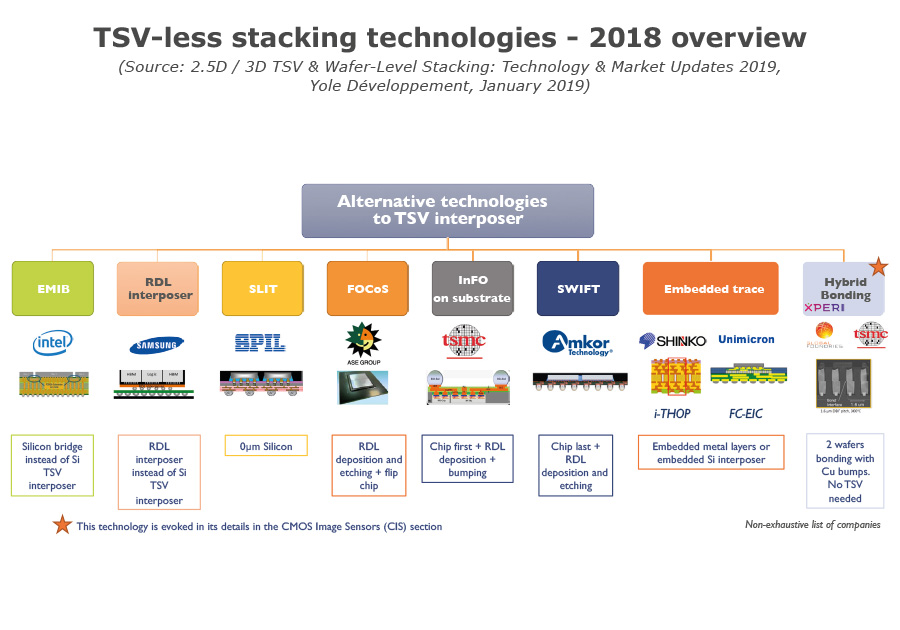

我們不能忽視“無TSV”技術的問世。這些創新可以分為兩類:帶基板型(with substrate)和埋入基板型(embedded in substrate)。埋入式多芯片互連橋接(EMIB)是已經商業化的埋入基板型技術,其硅橋深埋于基板。其他基板技術目前仍在開發尚未上市,如集成薄膜高密度有機封裝(I-THOP)和倒裝-埋入式轉接板技術(FC-EIC).

基板技術作為TSV的替代方案,如基板上集成扇出型封裝(InFO),廣泛用于蘋果(Apple)處理器。此外,RDL轉接板技術目前仍在開發,將于2020年上市。值得注意的是于2016年開發并商業化的基板扇出型芯片(FOCoS)技術,目前訂單并不多。

混合鍵合可以橋接“TSV”技術和“無TSV”技術,對于TSV而言,混合鍵合亦敵亦友。自2016年普遍運用至智能手機CIS,這項技術將于不久將來進入高端市場,成為存儲和2.5D的互連解決方案。

2018年無TSV型堆疊技術綜述

誰在支持并投資堆疊技術?

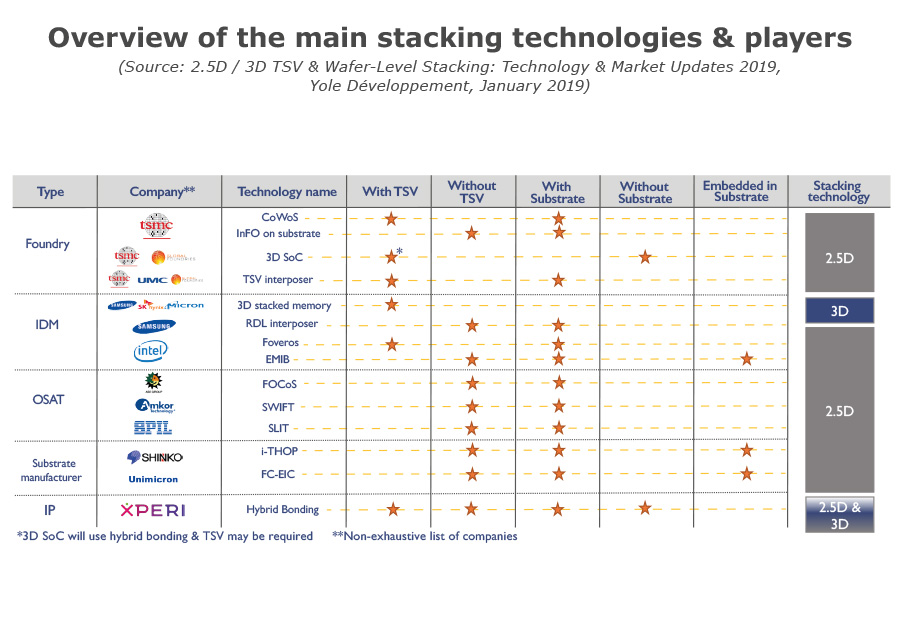

各類廠商都想從不斷增長的55億美元堆疊市場分一杯羹。目前,四類企業將參與競爭:代工廠、整合元件制造商、封測廠商和IP廠商。

因為有生產轉接板的能力,像臺積電、聯華電子、格芯半導體等晶圓代工廠將主導TSV異質堆疊技術。英特爾,憑借Foveros技術,是唯一嘗試競爭的整合元件制造商。3D堆疊存儲市場的競爭集中在三大整合元件制造商,三星、海力士和美光,并將繼續統治堆疊存儲市場。同時,3D SoC作為一種代工廠技術,很可能只有一家代工廠會生產,以確保高良率并控制風險。在這方面,臺積電的上市時間將領先于格芯。

對于無TSV技術的市場競爭,將更集中于代工廠、整合元件制造商、封測廠商和基板廠商之間。三星、英特爾、臺積電等廠商都開展了TSV技術和無TSV技術的研發。2016年,封測廠日月光推出了FOCoS技術,而安靠等其他廠商也開發了其他合適的技術,但仍在等訂單。

至于神鋼、欣興電子和最近的富士通Interconnect等基板廠商仍處于開發階段。IP廠商Xperi的混合鍵合技術,介于TSV技術和無TSV技術之間,預計將對市場產生積極影響。Xperi的其他優勢在于該技術可以兼容高端市場和中低端市場。

考慮到封測廠商獲取訂單較困難,代工廠、整合元件制造商和IP廠商在堆疊技術市場占有優勢。

堆疊技術和廠商綜述

報告目標:

闡述半導體市場變化對封裝技術的影響

概述三種堆疊技術:TSV、3D SoP和混合鍵合

綜述堆疊技術市場、市場數據和預測

描述采用堆疊技術的的硬件及關鍵應用

列舉堆疊技術的主要供應商和供應鏈

介紹可能挑戰堆疊技術的最新解決方案

預測堆疊技術應用領域

新的內容:

兩大主要細分市場:高端市場:HPC、網絡、AR、VR、MR等;中低端市場:CIS、MEMS、LED

半導體市場變化和對堆疊技術的影響

TSV在HPC和網絡硬件的應用

即將于2019年上市的3D SoC技術

混合鍵合/堆疊技術:市場、應用、預測和供應商

CIS領域的堆疊技術預測

挑戰2.5D TSV轉接板的技術

涉及企業:

Alchip, Aledia, Alibaba, Amazon, AMD, Amkor, AMS, ANPEC, Apple, ASE, ASUS, Atos, Audi,, Avago, Baidu, Bosch, Bitmain, BitFury, Broadcom, Canaan, Carsem, Cisco, Cray, DARPA, EBANG,, EMmicroelectronic, EPworks, Facebook, Faraday, Fingerprints, Foxconn, Fraunhofer, Fujitsu,, Gigabyte, GlobalFoundries, Google, GUC, HalongMining, HLMC, HP, Huatian, Huawei, Ibiden, IBM,, Icsens, IMEC, Inari Technology, Infineon, Innosilicon, Intel, InvenSense, JCET STATS ChipPAC, Juniper,, Lenovo, Leti, Lfoundry, LGinnotek, mCube, Melexis, Memsic, Mercedes-Benz, Micralyne, Micron, Microsoft, NEC, Nokia, Nvidia, NXP, Omnivision, ON Semiconductor, OpenSilicon, Osram, PTI,, Samsung, SensL, Shinko, SK Hynix, SMIC, Sony, SPIL, STMicroelectronics, Tencent, TF, Toshiba,, TPK, TSMC, UMC, Unimicron, Xfab, Xilinx, Xintek, XMC, Xperi, YMTC, and more…

華進擁有成熟先進的TSV技術,如有相關業務需求,歡迎聯系市場部呂經理0510-66679336。

獲知更多先進封裝市場進展,歡迎參加2019年NCAP & Yole Advanced Packaging and System Integration Symposium(上海浦東,4月22日-4月23日),與業內大咖面對面!

如需購買報告,請聯系華進戰略部:0510-66679351;

以上圖文譯自Yole Développement的2.5D / 3D TSV & Wafer-Level Stacking: Technology & Market Updates 2019,原文請參考:

https://www.i-micronews.com/produit/2-5d-3d-tsv-wafer-level-stacking-technology-market-updates-2019/

(戰略部)

中文

中文

English

English 蘇公網安備 32021402001899號

蘇公網安備 32021402001899號